|

Im

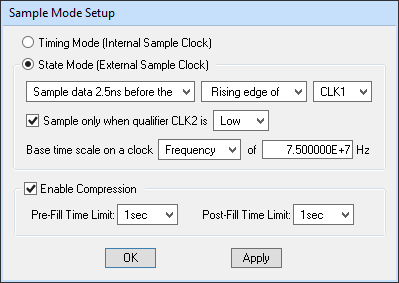

Timing-Modus speichert der LogicPort die Daten mittels der intern

generierten Clock-Signale. Der Anwender kann diese interne Clock-Rate

zwischen 1 KHz und 500 MHz wählen.

Im

State-Modus speichert der LogicPort die aktuellen Daten ab, wenn

sich die spezifizierte Flanke des Clock-Signals der zu prüfenden

Schaltung ändert. Der Sample-Zeitpunkt kann relativ zur Clock-Flanke

um +/-2.5ns verschoben werden, um Signale mit verschobenen Clocks

oder engen „Data Valid“-Fenstern zu erfassen. Dies ist eine Funktionalität,

die ansonsten nur in weitaus teureren Logikanalysatoren zu finden

ist. In diesem Beispiel wurde das Sample-Fenster modifiziert, so

dass nun die Daten 2,5ns vor dem Auftreten einer steigenden Flanke

des Clock-Signals aufgezeichnet wird. Das qualifizierte Sampling

ist ebenfalls aktiviert, so dass der LogicPort nur dann aufzeichnet,

wenn auch gleichzeitig das CLK2-Signal „low“ ist. Der qualifizierte

State-Modus ist sehr hilfreich, um einen Prozessor-Bus, der Daten

und Adressinformationen auf dem gleichen Bus multiplext, zu demultiplexen

– also z.B. nur die Dateninformationen herauszulesen und die Adressdaten

auf dem Bus zu ignorieren. Dieser Modus ist auch gut nutzbar, um

die Befehle an ein bestimmtes Peripheriegerät heraus zu filtern:

als Qualifier wird dann das Enable-Signal dieses Geräts genutzt.

Datenkompression

ist sowohl für den Timing-Modus als auch für den State-Modus verfügbar.

Wenn die Kompression eingeschaltet ist, erlauben die Parameter für

Pre-Fill und Post-Fill die Auswahl, wie lange Sie auf eine Datenakquisition

warten möchten. Dies ist in einer Umgebung hilfreich, in der nur

vereinzelte Signale auftreten oder in der lediglich zeitweilig Datenblöcke

anfallen. In solchen Situationen arbeitet die Datenkompression

extrem effektiv und es kann eine sehr lange Zeit dauern, bis die

Datenakquisition beendet wird. Unter bestimmten Umständen kann der

LogicPort mehrere Stunden lang Daten in den Sampling-Puffer packen. |