|

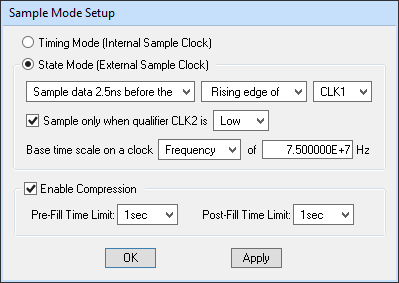

In timing mode, the LogicPort acquires samples using its

internally generated sample clock. The user can select a

desired rate from 1KHz to 500MHz for this internal clock. In state mode, the LogicPort samples on the specified

edge of an external clock supplied by the hardware under test. The LogicPort's Setup/Hold window is adjustable relative to

the clock input, a feature usually found only on much more

expensive units. The adjustable window provides greater flexibility when sampling high-speed signals

with tight timing margins. Notice that in this particular example the sample window has been adjusted to a position 2.5ns before the rising edge of the

external clock.

Qualified sampling has also been enabled, causing the

LogicPort to sample only when CLK2 is low. Qualified

state mode sampling is useful for de-multiplexing processor

buses which multiplex Address and Data information onto the

same bus. It can also be used to capture data directed

toward a particular peripheral by using the peripheral's

enable signal as a qualifier.

Sample compression is available for both timing mode and state mode. When compression is enabled, Pre-Fill and Post-Fill time limits allow you to specify how long you are willing to wait for an acquisition to complete. This is useful when the

hardware under test has few transitions or has intermittent bursts of activity. In these situations the sample compression ratio can be extremely high, and it could take a long time to complete an acquisition. Under certain circumstances the LogicPort can pack hours of data into

Its sample buffer! |